proizvodi Категорија

- ФМ предајник

- КСНУМКС-КСНУМКСв КСНУМКСв-КСНУМКСв КСНУМКСкв-КСНУМКСкв КСНУМКСкв +

- ТВ предајник

- КСНУМКС-КСНУМКСв КСНУМКС-КСНУМКСкв КСНУМКСкв-КСНУМКСкв

- ФМ антена

- ТВ Антена

- антена принадлежности

- кабл конектор Сплиттер думми лоад

- Транзистор рф

- Напајање

- Аудио Опрема

- ДТВ Фронт Енд опрема

- линк систем

- ЛИС систем Микроталасна Линк систем

- ФМ радио

- power Метер

- Остали производи

- Специјално за коронавирус

производи Тагс

Фмусер сајтови

- ес.фмусер.нет

- ит.фмусер.нет

- фр.фмусер.нет

- де.фмусер.нет

- аф.фмусер.нет -> африкаанс

- ск.фмусер.нет -> албански

- ар.фмусер.нет -> арапски

- хи.фмусер.нет -> Арменски

- аз.фмусер.нет -> азербејџански

- еу.фмусер.нет -> баскијски

- бе.фмусер.нет -> белоруски

- бг.фмусер.нет -> бугарски

- ца.фмусер.нет -> каталонски

- зх-ЦН.фмусер.нет -> кинески (поједностављени)

- зх-ТВ.фмусер.нет -> кинески (традиционални)

- хр.фмусер.нет -> хрватски

- цс.фмусер.нет -> чешки

- да.фмусер.нет -> дански

- нл.фмусер.нет -> холандски

- ет.фмусер.нет -> естонски

- тл.фмусер.нет -> филипински

- фи.фмусер.нет -> фински

- фр.фмусер.нет -> француски

- гл.фмусер.нет -> галицијски

- ка.фмусер.нет -> грузијски

- де.фмусер.нет -> немачки

- ел.фмусер.нет -> грчки

- хт.фмусер.нет -> хаићански креол

- ив.фмусер.нет -> хебрејски

- хи.фмусер.нет -> хинду

- ху.фмусер.нет -> мађарски

- ис.фмусер.нет -> исландски

- ид.фмусер.нет -> индонежански

- га.фмусер.нет -> ирски

- ит.фмусер.нет -> италијански

- ја.фмусер.нет -> јапански

- ко.фмусер.нет -> корејски

- лв.фмусер.нет -> летонски

- лт.фмусер.нет -> Литвански

- мк.фмусер.нет -> македонски

- мс.фмусер.нет -> малајски

- мт.фмусер.нет -> малтешки

- но.фмусер.нет -> норвешки

- фа.фмусер.нет -> перзијски

- пл.фмусер.нет -> пољски

- пт.фмусер.нет -> португалски

- ро.фмусер.нет -> румунски

- ру.фмусер.нет -> руски

- ср.фмусер.нет -> српски

- ск.фмусер.нет -> словачки

- сл.фмусер.нет -> Словеначки

- ес.фмусер.нет -> шпански

- св.фмусер.нет -> свахили

- св.фмусер.нет -> шведски

- тх.фмусер.нет -> Тајландски

- тр.фмусер.нет -> турски

- ук.фмусер.нет -> украјински

- ур.фмусер.нет -> урду

- ви.фмусер.нет -> Вијетнамски

- ци.фмусер.нет -> велшки

- ии.фмусер.нет -> јидиш

Шта је полусабирање: дијаграм кола и његове примене

Date:2021/10/18 21:55:58 Hits:

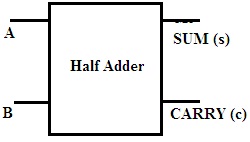

Half Adder je vrsta osnovnog digitalnog kola. Ranije su se u analognim krugovima izvodile različite operacije. Nakon otkrića digitalne elektronike, u njoj se vrše slične operacije. Digitalni sistemi se smatraju efikasnim i pouzdanim. Među raznim operacijama, jedna od najistaknutijih operacija je Aritmetička. Uključuje sabiranje, oduzimanje, množenje i deljenje. Međutim, već je poznato da bi to mogao biti računar, bilo koji elektronski uređaj poput kalkulatora može da obavlja matematičke operacije. Ove operacije se izvode sastoje se od binarnih vrednosti. To je moguće prisustvom određenih kola u njemu. Ova kola se nazivaju binarni sabirači i oduzimači. Ova vrsta kola je dizajnirana za binarne kodove, Excess-3 kodove i druge kodove. Dalji binarni sabirci su klasifikovani u dva tipa. To su: Half sabirač i puni sabirač Šta je polusabirač? Digitalno elektronsko kolo koje funkcioniše da izvrši sabiranje binarnih brojeva je definisano kao polusabirač. Proces sabiranja je denar, jedina razlika je izabrani sistem brojeva. U binarnom sistemu numerisanja postoje samo 0 i 1. Težina broja je u potpunosti zasnovana na pozicijama binarnih cifara. Među tim 1 i 0, 1 se tretira kao najveća cifra, a 0 kao manja. Blok dijagram ovog sabirača je Dijagram kola polu-sabirača-polubirača Polu-sabirač se sastoji od dva ulaza i proizvodi dva izlaza. Smatra se da su najjednostavnija digitalna kola. Ulazi u ovo kolo su bitovi na kojima treba izvršiti sabiranje. Dobijeni rezultati su zbir i prenos.

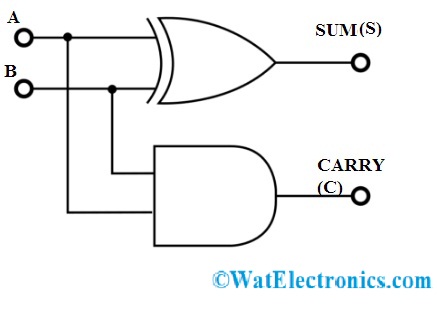

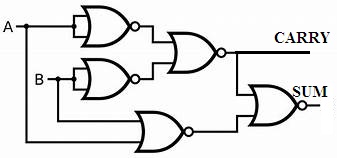

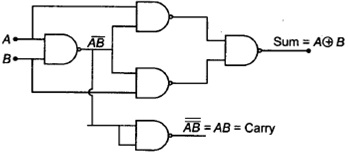

Dijagram kola polu-sabirača-polubirača Polu-sabirač se sastoji od dva ulaza i proizvodi dva izlaza. Smatra se da su najjednostavnija digitalna kola. Ulazi u ovo kolo su bitovi na kojima treba izvršiti sabiranje. Dobijeni rezultati su zbir i prenos.  Polu sabirač Kolo ovog sabirača sastoji se od dve kapije. To su AND i XOR kapije. Primenjeni ulazi su isti za obe kapije prisutne u kolu. Ali izlaz se uzima sa svake kapije. Izlaz XOR kapije se naziva SUM, a izlaz AND je poznat CARRY. Half Adder Truth Table Da bi se dobio odnos dobijenog izlaza i primenjenog ulaza, može se analizirati korišćenjem tabele poznate kao Tabela istine.

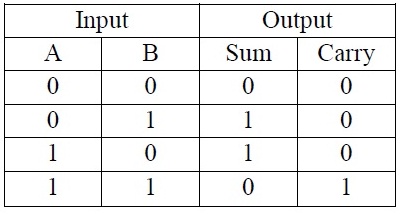

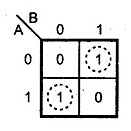

Polu sabirač Kolo ovog sabirača sastoji se od dve kapije. To su AND i XOR kapije. Primenjeni ulazi su isti za obe kapije prisutne u kolu. Ali izlaz se uzima sa svake kapije. Izlaz XOR kapije se naziva SUM, a izlaz AND je poznat CARRY. Half Adder Truth Table Da bi se dobio odnos dobijenog izlaza i primenjenog ulaza, može se analizirati korišćenjem tabele poznate kao Tabela istine. Tabela istinitosti polusabirača Iz gornje tabele istinitosti tačke su evidentne na sledeći način: Ako je A=0, B=0 to su oba primenjena ulaza su 0. Tada su oba izlaza SUM i CARRY 0. Među dva primenjena ulaza ako je bilo ko ulaz je 1, onda će ZBIR biti e1, ali CARRY je 0. Ako su oba ulaza 1, onda će ZBIR biti jednak 0, a CARRY će biti jednak 1. Na osnovu primenjenih ulaza, polusabirač nastavlja sa operacijom jednačine.Jednačina Jednačina za ovu vrstu kola može se realizovati konceptima zbira proizvoda (SOP) i proizvoda zbira (POS). Bulova jednačina za ovu vrstu kola određuje odnos između primenjenih ulaza i dobijenih izlaza. Da bi se odredila jednačina, k-mape se crtaju na osnovu vrednosti tabele istinitosti. Sastoji se od dve jednačine jer se u njemu koriste dve logičke kapije. K-mapa prenosa je

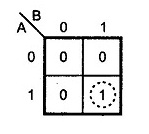

Tabela istinitosti polusabirača Iz gornje tabele istinitosti tačke su evidentne na sledeći način: Ako je A=0, B=0 to su oba primenjena ulaza su 0. Tada su oba izlaza SUM i CARRY 0. Među dva primenjena ulaza ako je bilo ko ulaz je 1, onda će ZBIR biti e1, ali CARRY je 0. Ako su oba ulaza 1, onda će ZBIR biti jednak 0, a CARRY će biti jednak 1. Na osnovu primenjenih ulaza, polusabirač nastavlja sa operacijom jednačine.Jednačina Jednačina za ovu vrstu kola može se realizovati konceptima zbira proizvoda (SOP) i proizvoda zbira (POS). Bulova jednačina za ovu vrstu kola određuje odnos između primenjenih ulaza i dobijenih izlaza. Da bi se odredila jednačina, k-mape se crtaju na osnovu vrednosti tabele istinitosti. Sastoji se od dve jednačine jer se u njemu koriste dve logičke kapije. K-mapa prenosa je  K-Mapa AND Gate Izlazna jednačina CARRY se dobija iz kapije AND. C=A.B Bulov izraz za zbir se realizuje pomoću SOP obrasca. Otuda je K-mapa za SUM

K-Mapa AND Gate Izlazna jednačina CARRY se dobija iz kapije AND. C=A.B Bulov izraz za zbir se realizuje pomoću SOP obrasca. Otuda je K-mapa za SUM K-Mapa za zbir (XOR) Određena jednačina je S= A⊕ BA. Primene Primene ovog osnovnog sabirača su sledeće. Za obavljanje sabiranja binarnih bitova aritmetička i logička jedinica prisutna u računaru preferiraju ovo kolo sabirača. do formiranja kola sa punim sabiračem. Ova logička kola su poželjna u dizajnu kalkulatora. Za izračunavanje adresa i tabela ova kola su poželjna. Umesto samo sabiranja, ova kola su sposobna za rukovanje različitim aplikacijama u digitalnim kolima. Dalje, ovo postaje srce digitalne elektronike. VHDL kod VHDL kod za biblioteku kola pola sabirača ieee;koristite ieee.std_logic_1164.all;entity half_adder isport(a,b: in bit; sum,carry:out bit);end half_adder ;podaci o arhitekturi half_adder-a isbeginsum<= a xor b;carry <= a and b;end data;FAQs1. Šta mislite pod sabiračem? Digitalna kola čija je jedina svrha da obavljaju sabiranje poznata su kao sabirači. Ovo su glavne komponente ALU-a. Sabirači rade pored različitih formata brojeva. Izlazi sabirača su zbir i nosi.2. Koja su ograničenja polu-sabirača? Prenosni bit generisan iz prethodnog bita ne može se dodati je ograničenje ovog sabirača. Za obavljanje sabiranja za više bitova ova kola ne mogu biti poželjna.3. Kako implementirati Half sabirač koristeći NOR kapiju? Implementacija ovog tipa sabirača se takođe može obaviti korišćenjem NOR kapije. Ovo je još jedna Univerzalna kapija.

K-Mapa za zbir (XOR) Određena jednačina je S= A⊕ BA. Primene Primene ovog osnovnog sabirača su sledeće. Za obavljanje sabiranja binarnih bitova aritmetička i logička jedinica prisutna u računaru preferiraju ovo kolo sabirača. do formiranja kola sa punim sabiračem. Ova logička kola su poželjna u dizajnu kalkulatora. Za izračunavanje adresa i tabela ova kola su poželjna. Umesto samo sabiranja, ova kola su sposobna za rukovanje različitim aplikacijama u digitalnim kolima. Dalje, ovo postaje srce digitalne elektronike. VHDL kod VHDL kod za biblioteku kola pola sabirača ieee;koristite ieee.std_logic_1164.all;entity half_adder isport(a,b: in bit; sum,carry:out bit);end half_adder ;podaci o arhitekturi half_adder-a isbeginsum<= a xor b;carry <= a and b;end data;FAQs1. Šta mislite pod sabiračem? Digitalna kola čija je jedina svrha da obavljaju sabiranje poznata su kao sabirači. Ovo su glavne komponente ALU-a. Sabirači rade pored različitih formata brojeva. Izlazi sabirača su zbir i nosi.2. Koja su ograničenja polu-sabirača? Prenosni bit generisan iz prethodnog bita ne može se dodati je ograničenje ovog sabirača. Za obavljanje sabiranja za više bitova ova kola ne mogu biti poželjna.3. Kako implementirati Half sabirač koristeći NOR kapiju? Implementacija ovog tipa sabirača se takođe može obaviti korišćenjem NOR kapije. Ovo je još jedna Univerzalna kapija. Pola sabirača koristeći NOR kapije4. Kako implementirati Half Adder koristeći NAND kapiju? NAND kapija je jedna od vrsta univerzalnih kapija. To ukazuje da je bilo koja vrsta projektovanja kola moguća upotrebom NAND kapija.

Pola sabirača koristeći NOR kapije4. Kako implementirati Half Adder koristeći NAND kapiju? NAND kapija je jedna od vrsta univerzalnih kapija. To ukazuje da je bilo koja vrsta projektovanja kola moguća upotrebom NAND kapija. Half Adder Iz gornjeg kola, izlaz za nošenje se može generisati primenom izlaza jedne NAND kapije na ulaz kao druge NAND kapije. To nije ništa drugo nego poznato izlazu dobijenom iz AND kapije. Izlazna jednačina SUM može biti generisana primenom izlaza inicijalne NAND kapije zajedno sa pojedinačnim ulazima A i B na dalje NAND kapije. Konačno, izlazi dobijeni od tih NAND kapija se ponovo primenjuju na kapiju. Stoga se generiše izlaz za SUM. Zbog toga se osnovni sabirač u digitalnom kolu može dizajnirati korišćenjem različitih logičkih kapija. Ali sabiranje više bitova postaje komplikovano i smatra se ograničenjem polusabirača. Možete li opisati koji IC se koristi za operaciju povećanja u bilo kojim praktičnim brojačima?

Half Adder Iz gornjeg kola, izlaz za nošenje se može generisati primenom izlaza jedne NAND kapije na ulaz kao druge NAND kapije. To nije ništa drugo nego poznato izlazu dobijenom iz AND kapije. Izlazna jednačina SUM može biti generisana primenom izlaza inicijalne NAND kapije zajedno sa pojedinačnim ulazima A i B na dalje NAND kapije. Konačno, izlazi dobijeni od tih NAND kapija se ponovo primenjuju na kapiju. Stoga se generiše izlaz za SUM. Zbog toga se osnovni sabirač u digitalnom kolu može dizajnirati korišćenjem različitih logičkih kapija. Ali sabiranje više bitova postaje komplikovano i smatra se ograničenjem polusabirača. Možete li opisati koji IC se koristi za operaciju povećanja u bilo kojim praktičnim brojačima?

Остави поруку

Листа порука

Коментари Учитавање ...